# <u>Onsemí</u>,

# FAD3151MXA, FAD3171MXA Gate Driver Application Note

110 V 2.5 A Single Channel Floating Gate Drivers with Desaturation Protection and Charge Pump

# AND90251/D

The FAD3151MXA and FAD3171MXA are single channel floating automotive gate drivers suitable for driving high–speed power MOSFETs up to 110 V. Designed in a SOI technology, the drivers are ideal for applications that require noise immunity against severe negative transients and ground offset up to -80 V.

The FAD3151MXA/71 drivers have an integrated desaturation detection to protect the power switches during short–circuit and over–current conditions. The drivers are also equipped with a soft shutdown feature, which initiates a soft shutdown of driver outputs upon desaturation detection, thus preventing possible overvoltage across power MOSFETs during a heavy–load condition.

The FAD3151MXA/71 drivers are equipped with bidirectional fault reporting pin that generates a fault output during desat and under–voltage lockout (UVLO) condition and at the same time acts as a shutdown/disable pin for the driver. The FLT pin is in a pulled–up state for normal operation. The gate driver pulls down the FLT pin internally during desat and under–voltage lockout condition. The bidirectional nature of the fault–reporting pin allows the driver to respond to external fault commands and giving status feedback saving one pin. In addition, the FAD3171MXA has an integrated charge pump to support 100% duty cycle operation of high side MOSFETS.

In summary, the FAD3151MXA/71 are versatile drivers with features like desat detection, soft shutdown, fault reporting capability, UVLO protection, and charge pump.

### Features

- Single Channel Gate Driver with +/-110 V Floating Vs Capability

- 2.5 A Output Source and Sink Current

- MOSFET Drain–Source Desaturation Detection with Soft Shutdown

- Integrated Charge Pump to Support 100% Duty Cycle Operation (FAD3171 Only)

- Under-voltage Lockout for Both Input Logic and Output Stage

- Bi-directional Fault Reporting Pin

- High Speed Driver with Short Propagation Delay

- $dV_s/dt$  Immune to Min ±50 V/ns

- 3.3 V and 5 V Input Logic Compatible

- Up to V<sub>DD</sub> Swing on Input Pins

- SOIC–8 Package

- Pb–Free and RoHS compliant

- Automotive Qualified to AEC Q100

#### **Typical Applications**

- Gate Driver for 80 V and 100 V MOSFETs and Modules

- 48 V Belt Starter Generator

- 48 V Auxiliary Motor Control (A/C Compressor, e–Turbo, ...)

- 48 V Battery Switches

- 48 V DC–DC Converter

- PTC Heaters

- Active DC-Link Discharge Circuits

Figure 1. SOIC-8 (Case 751EB)

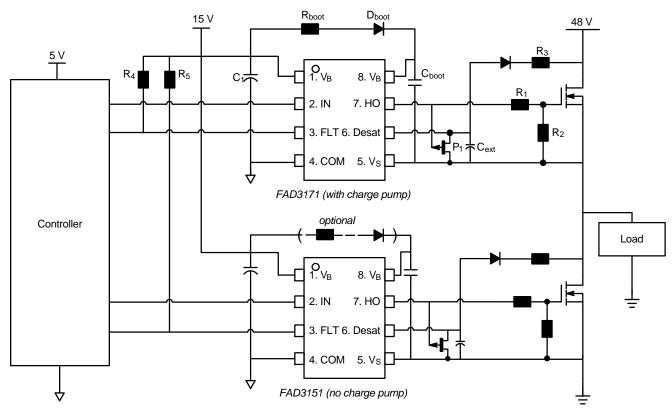

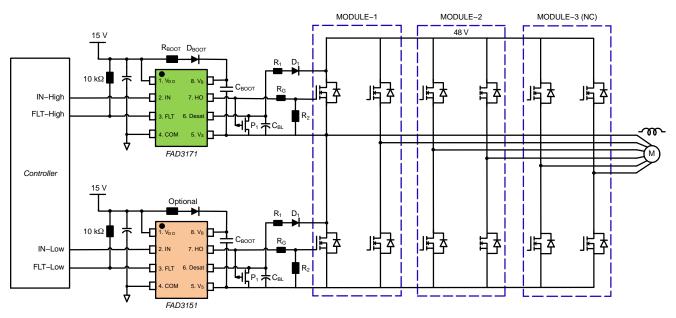

Figure 2. Application Schematic with FAD3171 as High Side and FAD3151 as Low Side Drivers

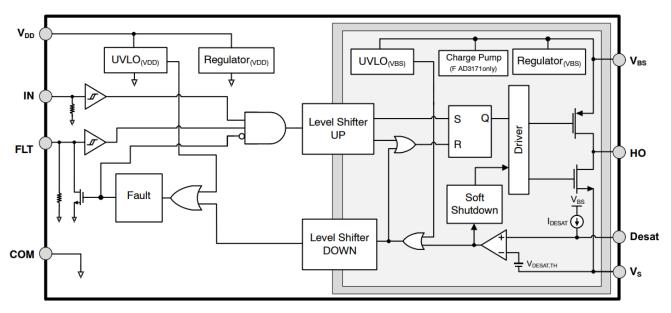

Figure 3. FAD3151 and FAD3171 (with Charge Pump) Simplified Block Diagram

## **PIN FUNCTION DESCRIPTION**

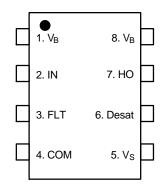

### Figure 4. Pin Connection (Top View)

### **PIN DESCRIPTION**

| Pin No. | Symbol          | Description                                |

|---------|-----------------|--------------------------------------------|

| 1       | V <sub>DD</sub> | Power supply for logic stage               |

| 2       | IN              | Input command                              |

| 3       | FLT             | Bi-directional Fault pin                   |

| 4       | СОМ             | Ground for logic stage                     |

| 5       | VS              | Floating source connection                 |

| 6       | Desat           | Drain to Source Desaturation detection pin |

| 7       | НО              | Output                                     |

| 8       | VB              | Floating Power Supply for power stage      |

#### **APPLICATION EXAMPLES**

#### Gate Driver for 48 V DC–DC Converter Battery Switch

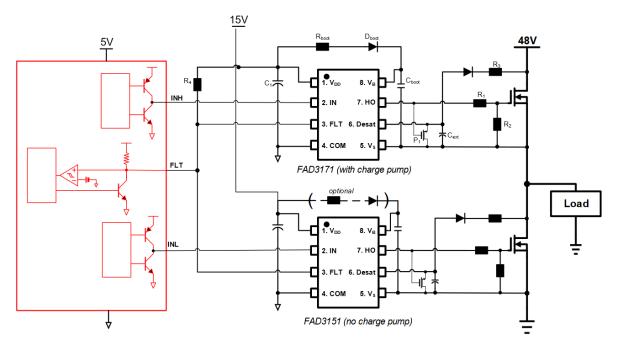

The simplified block diagram in Figure 5 shows how the FAD3171 can be used to drive a MOSFET as a battery main switch in a 48 V DC–DC converter.

The initial turn-on of the MOSFET is done through the bootstrap capacitance, initially charged by the 15 V supply. The integrated charge pump in the FAD3171 does not have enough source current capability to assure a direct energy efficient turn on of a larger die size MOSFET.

Once the MOSFET is turned on with 100% duty cycle, the bootstrap capacitance cannot charge any more through the 15 V supply and gets depleted by the continuous current sink into the gate to source resistance  $R_2$  and by the internal leakage current of the gate driver.

The charge pump integrated in the FAD3171 turns on as soon as the bootstrap voltage drops below the charge pump turn on threshold, typ. 10.8 V. The charge pump operates and supplies current until the bootstrap voltage reaches the upper charge pump turn off threshold voltage (typ. 11.2 V) or, in case current consumption is too high, the bootstrap voltage drops to the driver turn off level of typ. 7.5 V.

Note that to minimize the leakage current in the gate path, the resistance  $R_2$  should not be too low. Considering the 200  $\mu$ A current sourced by the charge pump at 9 V, excluding the desat current, the resistance  $R_2$  should be greater than 47 k $\Omega$  to maintain 9 V on the gate of the MOSFET.

Figure 5. Gate Driver for 48 V Battery Switch

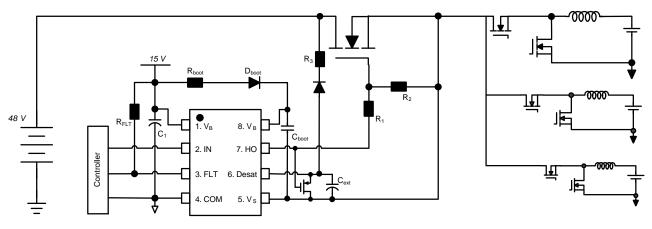

Figure 6. Gate Driver for 48 V, 3-module 6-phase Motor Control Application Circuit

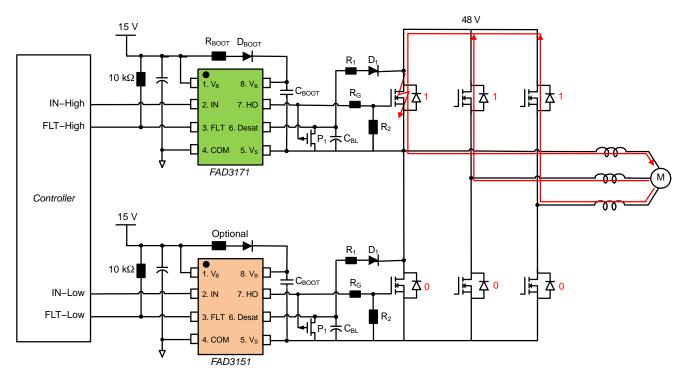

Figure 7. Gate Driver in a 3-phase Motor Control Application Circuit Operating in Active System Protection

# Gate Driver for High Power Motor Control, Configured for Active System Protection

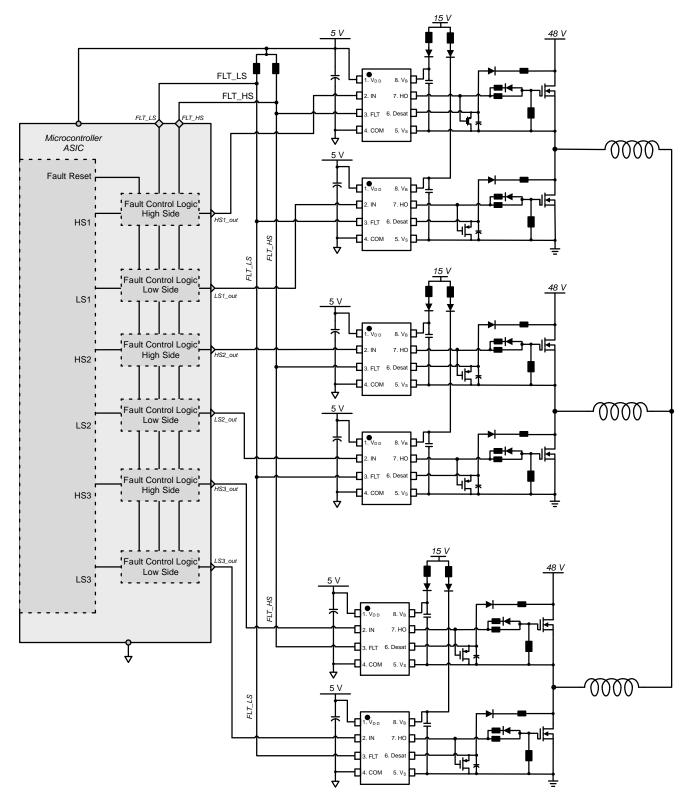

The block diagram in Figure 8 shows an example of motor control application such as a 48 V belt starter generator (BSG). The fault pins of different gate drivers are interconnected together to allow a short reaction time to turn off the affected channels upon a fault detection.

To allow current generated by the motor to discharge in the motor winding, the active turn on of the opposite channels can be programmed within the microcontroller with a simple logic as shown in Figure 8. The operation is summarized below:

- The fault pins of all High Side gate drivers are interconnected together; a fault on the High Side will:

- Turn off all High Side gate driver outputs (controlled by the gate driver FLT\_HS pins)

- Turn on all Low Side gate driver outputs (controlled by the microcontroller control logic)

- The fault pins of all Low Side gate drivers are interconnected together; a fault on the Low Side will:

- Turn off all Low Side gate driver outputs (controlled by the gate driver FLT\_LS pins)

- Turn on all High Side gate driver outputs (controlled by the microcontroller control logic)

- Faults on both the High Side and the Low Side gate drivers will:

- Turn off both the High Side and Low Side gate driver outputs (controlled by the gate driver FLT\_HS and FLT\_LS pins)

- To reset the fault in this case, the fault signals in the microcontroller should be bypassed with a FLT\_Reset signal to allow the microcontroller to send a positive pulse on its output

By tying all fault pins together on high side or low side, an active system short–circuit protection can be achieved. During active system fault protection, either all high side or all low side switches are turned on to allow the load current to freewheel preventing overvoltage conditions and disturbances in the 48 V supply network and at the same time bringing the motor to safe state. Please refer to current flow in Figure 7.

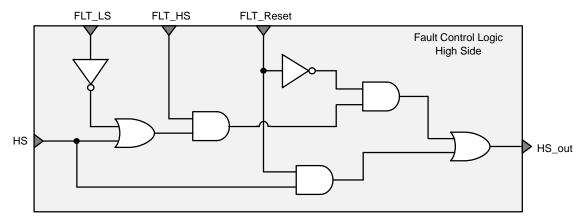

#### **Example of a Fault Control Logic**

The Fault control logic in Figure 8 to allow active discharge is explained below:

#### Figure 8. Example of Fault Control Logic High Side to Enable Active Discharge of Phase Current in Motor Winding

FLT\_Reset is at 0 in all operation, except when a fault needs to be cleared

- If no fault on HS, FLT\_HS=1

- If no fault on the Low Side, FLT\_LS=1, then HS\_out=HS

- If fault on the Low Side, FLT\_LS=0, then HS\_out=1 (active turn on)

- If Fault on HS, FLT\_HS=0, then Phase\_HS\_out=0 (no active turn on for channels that have a fault)

In case both High Side and Low Side gate drivers are in fault mode, then it is not possible to apply a positive pulse on any input to clear a fault. The FLT\_Reset command is used to bypass the faults and allow to apply a pulse on the input of the gate drivers to clear a fault:

• If FLT-Reset=1, then HS\_out=HSFLT\_LS FLT\_HS

# Microcontroller Interface to the Gate Driver's IN and FLT Pins

The microcontroller must have a pull up and a pull down output stage to set the input of the gate driver to high and to low. The microcontroller should, however, be able to pull up and pull down the gate driver FLT pin. It should also be able to adopt a high impedance state since the gate driver itself is able to trigger a fault by pulling down the FLT pin. This can be done with a simple pull down stage combined with a comparator to monitor the state of the FLT pin.

#### Figure 9. Microcontroller I/O Interface with the Gate Driver

Figure 10. Block Diagram with Fault Pins Interconnected for Fault Communication

#### **Bootstrap Drive Circuit Operation**

Both the FAD3151 and the FAD3171 normally use the bootstrap technique to achieve an elevated gate drive voltage in high side operation. This bootstrap power supply technique has the advantage of being simple and low cost. However, it has some limitations. On time of duty–cycle it is limited by the time required to refresh the charge in the bootstrap capacitor.

To overcome these limitations, the FAD3171MXA driver contains an internal charge pump that enables 100% duty cycle operation of high side power switches. When the high side switch is kept on for a long duration, the bootstrap capacitor could slowly discharge and may eventually trigger the undervoltage lockout protection and turn off the driver output. Therefore, the purpose of the charge pump is to supply the V<sub>BS</sub> quiescent current necessary for the high side gate driver to operate under 100% duty cycle and to compensate for additional leakage current on the gate path.

It should be ensured that the total leakage current in the gate path does not exceed the maximum output current capability of the charge pump,  $I_{CP,OUT}$ .

It is important to note that the charge pump is not intended to provide gate charge during switching of a power MOSFET; rather its purpose is to only keep the MOSFET turned on. For this, it should be ensured at the system level that the high side MOSFET is not operated at very high duty cycle or, if a high duty cycle operation is required, the off time should be long enough to allow the bootstrap capacitor on high side gate driver to completely recharge. In order to minimize continuous power dissipation, the charge pump turns on only when needed, and remains off at other times.

For details on the bootstrap gate-drive circuit requirements of the power MOSFET and IGBT in various switching-mode power-conversion applications and the dimensioning of the components, please refer to AN-6076: Design and Application Guide of Bootstrap Circuit for High-Voltage Gate-Drive IC. <u>AND9674/D</u> (onsemi.com)

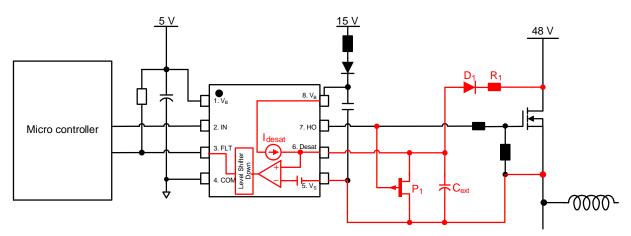

#### **Desaturation Protection Circuit**

In order to protect the power stage from overload or short circuit, the FAD3151/71 features desaturation detection, which works as follows:

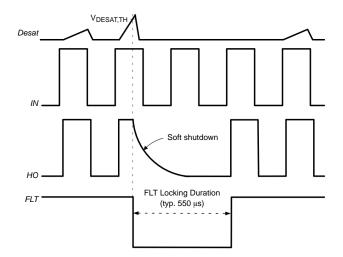

An internal constant current source,  $I_{desat}$ , charges an external capacitor connected to the desat pin. This allows a programmable blanking delay during every ON cycle before desat fault is processed, thus preventing false triggering. When the desat voltage goes up and reaches the desaturation threshold,  $V_{desat+}$ , the output is driven low. Further, the FLT output is activated. Please refer to data sheet Figure 19 or Figure 11 below.

Figure 11. Desaturation Protection and Soft Shutdown

The desat terminal of the gate–driver IC monitors the drain–source voltage,  $V_{DS}$ , of the MOSFET continuously. In the event of an overcurrent or short circuit condition, the desat terminal detects a rise in  $V_{DS}$  voltage. If the desat terminal voltage exceeds  $V_{desat+}$  the gate driver IC generates a fault status and turns off the gate–drive output HO. The desat diode  $D_1$ , resistor  $R_1$ , blanking capacitor  $C_{ext}$ , and P–channel JFET  $P_1$  are the external components required to operate the desaturation protection scheme as shown in Figure 12.

- When the gate output HO is turned off, the "normally on" discharge transistor,  $P_1$ , provides an alternate path to the desat current source,  $I_{desat}$ , and prevents it from charging the external capacitor,  $C_{ext}$ . This ensures that the desat terminal voltage is always below the desat threshold and the fault signal is not triggered during off state.

- When the gate output HO is turned on, at a voltage above ~6 V, the P–JFET, P<sub>1</sub>, turns off. This allows the I<sub>desat</sub> to charge the external capacitor, which forms a parallel circuit with D<sub>1</sub>, R<sub>1</sub> and the drain to source of the MOSFET. After a period of time, t<sub>bl</sub>, the desat terminal voltage, V<sub>desat</sub>, stabilizes at the same level as the V<sub>DS</sub> of the MOSFET plus the forward voltage of the diode D<sub>1</sub> and the voltage drop across the resistor R<sub>1</sub>.

$$V_{desat} = V_{DS} + (V_{f} + R_{1} \times I_{desat})$$

(eq. 1)

• During normal operation, the V<sub>desat</sub> is below the V<sub>desat+</sub> and the fault pin remains disabled. During overcurrent condition, the drain to source voltage of the MOSFET rises causing the desat terminal voltage to rise as well. If the desat terminal voltage exceeds V<sub>Desat+</sub>, which is defined in the internal comparator stage, the gate driver generates a fault and turns off its output HO, independent of the status of the input pin. The parameters of the desat protection circuit can be adjusted as follows:

1. The desat detection must remain disabled for a short time period called blanking time to prevent false triggering while the MOSFET first turns on. The external blanking capacitor and the desat threshold can set the blanking time. The greater the selected  $C_{ext}$ , the greater the blanking time,  $t_{bl}$ .

$$t_{bl} = C_{ext} \times V_{desat+} / I_{desat}$$

(eq. 2)

Figure 12. Desaturation Protection Circuit

- 2. The actual  $V_{DS}$  threshold on the MOSFET side can be modified by

- Using a higher value of resistance R<sub>1</sub>: With a higher R<sub>1</sub>, the voltage at desat terminal can rise to its desat threshold at a lower V<sub>DS</sub> threshold of the MOSFET. This engages desat protection at a lower V<sub>DS</sub> threshold of the MOSFET. Remember:

$$V_{desat} = V_{DS} + (V_f + R_1 \times I_{desat})$$

(eq. 3)

- The selection of the desat diode is important. The desat protection works perfectly with a 200 V, 200 mA diode, which has a very low junction capacitance. When in experiments it was replaced with a generic 100 V, 1 A Schottky diode, a negative voltage spike was found to appear on the desat pin due to higher junction capacitance of this diode.

- NOTE: A low junction capacitance of the desat diode is essential for proper operation of the desat function under all operating conditions.

- Adding multiple series diodes: Adding diodes in series can engage desat protection at a lower V<sub>DS</sub> threshold of the MOSFET. However, the drawback is an additional increase in reverse recovery currents during turn-off of these diodes. The desat terminal voltage, V<sub>desat</sub>, with series diodes can be expressed as:

$$V_{desat} = V_{DS} + (n \times V_{f} + R_{1} \times I_{desat})$$

(eq. 4)

where n is the number of diodes.

During off state (HO low) the desat function is immune to any noise like that of capacitive coupling from adjacent switches the normally on PFET pulls the desat pin to ground. As a result, the desat pin is immune to noises when complementary FETs switches turn on and is not prone to spurious triggering.

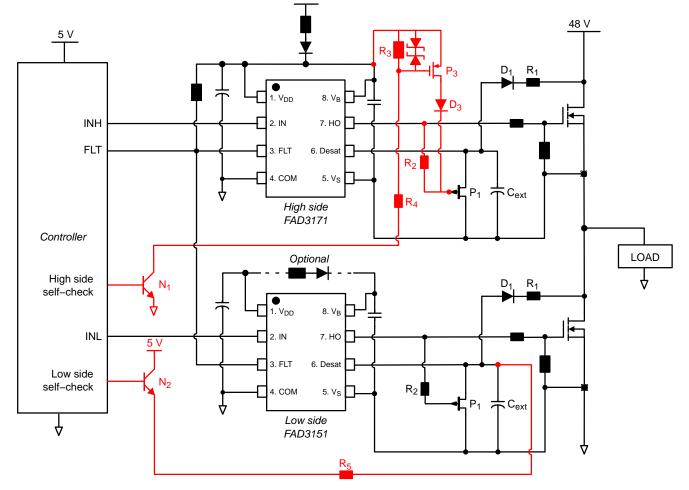

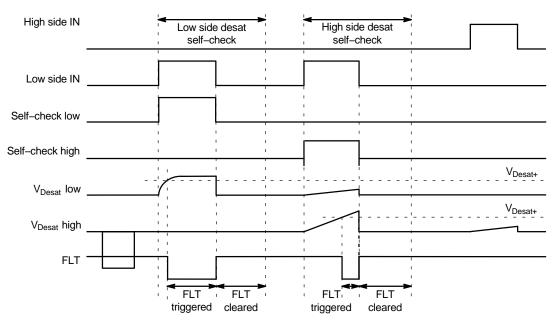

# Method for Checking the Proper Operation of the Desaturation Protection Circuit During Startup

To comply with functional safety requirements, the system might need to verify the proper operation of the desaturation protection circuit during startup. Figure 10 shows the external components necessary to perform a self-check of the desat protection circuit during startup.

- During normal operation, the self-check transistors (N<sub>1</sub> in high side and N<sub>2</sub> in low side) are turned off and the gate of P<sub>1</sub> is controlled by the respective gate driver output HO.

- When HO is low, the "normally on" P<sub>1</sub> keeps the Cext discharged by default. As a result, the desat protection is disabled.

- When HO is high, the gate of P<sub>1</sub> is pulled high through R<sub>2</sub>, causing P<sub>1</sub> to turn off. As a result, Cext is free to charge and engage in desat protection.

- During self-check mode of high side gate driver, the output of the gate driver HO should be turned off and the Vs pin should be set to ground. The Vs pin can be pulled to ground by turning on the low side gate driver.

- The self-check sequence for high side desat protection circuit is as follows: (please refer to the high side components in Figure 10 and the self-check sequence in Figure 11 for details.)

- i. The microcontroller provides a high side self-check signal to turn on transistor  $N_1$ .

- ii. The PMOS P<sub>3</sub> turns on and pulls up the gate voltage of P<sub>1</sub> to  $V_{DD}$  (= 15 V) through the path  $V_{DD}$ -P<sub>3</sub>-D<sub>3</sub>. As a result, P<sub>1</sub> turns off.

- iii. When P<sub>1</sub> turns off, the desat current flows into Cext and charges it until the voltage at the desat terminal rises to the desat threshold, Vdesat+. When Vdesat exceeds the internal Vdesat+, a fault status is triggered at the FLT pin of high side driver.

- iv. The fault status is cleared when the self-check signal for high side driver is turned off.

- A malfunction of the high side desat protection circuit is detected:

- if the high side gate driver is unable to trigger (set) a fault status on the FLT pin during self-check, or

- if the gate driver is unable to clear this fault status at the end of self-check.

- During self-check mode of low side gate driver, the output of the high side gate driver should be turned off. The self-check sequence for low side desat protection circuit is as follows: (Please refer to the low side components in Figure 13 and the self-check sequence in Figure 14 for details.)

- i. The microcontroller provides a low side self-check signal to turn on transistor N<sub>2</sub>. At the same time, the

output of the low side gate driver is turned on. As a result,  $P_1$  turns off.

- ii. When  $P_1$  turns off, both the  $I_{CE}$  of  $N_2$  and Idesat can charge Cext. In comparison to Idesat, the  $I_{CE}$  of  $N_2$  could be significantly higher. Therefore, Cext is rapidly charged. When Vdesat is higher than Vdesat+, a fault status is triggered at the FLT pin of low side driver.

- iii. The fault status is cleared when the self-check signal and the input signal for low side driver are turned off.

- A malfunction of the low side desat protection circuit is detected:

- if the low side gate driver is unable to trigger (set) a fault status on the FLT pin during self-check, or

- if the low side gate driver is unable to clear this fault status at the end of self-check.

- NOTE: The desat self-check circuit shown for high side can also be adopted for low side. The low side desat self-check circuit shown in Figure 13 has fewer components than the self- check circuit on high side.

Figure 13. Circuit to Perform Self-check of the Desaturation Protection During Startup

Figure 14. Self-check Sequence for High Side and Low Side Gate Driver

#### **Considerations for Safety Critical Applications**

For systems requiring functional safety, it is necessary to identify systematic failure modes that could compromise the safety of the system. The desat protection and its self-check circuit as explained in the previous chapter should be able to detect and protect against single-point failures of safety critical components. **onsemi** can support the integration into customer's safety applications with a set of safety documents including FMEDA on request.

| Table 1. FAILURE MODE ANALYSIS OF THE DESAT PROTECTION CIRCUIT |

|----------------------------------------------------------------|

|                                                                |

| Component        | Failure Mode | Effect and Diagnosis of Failure                                                                                                                                             | Behavior                                                                                                                                                                                                                                             |

|------------------|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| R <sub>1</sub>   | Open         | Triggers a systematic desat fault condition when HO is turned on.                                                                                                           | Safe                                                                                                                                                                                                                                                 |

|                  | Short        | Engages desat protection at a higher V <sub>DS</sub> threshold of the MOSFET.                                                                                               | <ul> <li>Risk</li> <li>Despite the failure, the system can operate without issue.</li> <li>Mitigation:<br/>Adding two resistances in series could be an option to ensure that a single point failure does not result in a safety concern.</li> </ul> |

| D <sub>1</sub>   | Open         | Triggers a systematic desat fault condition when HO is turned on.                                                                                                           | Safe                                                                                                                                                                                                                                                 |

|                  | Short        | Exposes the desat pin to high voltage and could damage the gate driver.                                                                                                     | <ul> <li>Risk</li> <li>Mitigation:<br/>Adding two diodes in series could be an option<br/>to ensure that a single point failure does not re-<br/>sult in a safety concern.</li> </ul>                                                                |

| C <sub>ext</sub> | Open         | Eliminates the blanking time and causes an<br>inadvertent triggering of desat fault during turn on<br>of MOSFET.                                                            | Safe                                                                                                                                                                                                                                                 |

|                  | Short        | <ul><li>Does not allow the desat pin to reach desat<br/>threshold.</li><li>Triggers a desat fault during self-check at start up.</li></ul>                                  | Safe                                                                                                                                                                                                                                                 |

| P <sub>1</sub>   | Open         | C <sub>ext</sub> is unable to discharge; triggers a systematic desat fault condition.                                                                                       | Safe                                                                                                                                                                                                                                                 |

|                  | Short        | Does not allow the desat pin to reach its desat<br>threshold during self-check; this can be detected<br>during self-check as a fault status is triggered on<br>the FLT pin. | Safe                                                                                                                                                                                                                                                 |

| Component      | Failure Mode | Effect and Diagnosis of Failure                                                                                                                                                                                                                                                           | Behavior |

|----------------|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| D <sub>3</sub> | Open         | <ul> <li>Does not allow P<sub>1</sub> to turn off during self– check;<br/>this can be detected during self– check as a<br/>fault status is triggered on the FLT pin.</li> </ul>                                                                                                           | Safe     |

|                | Short        | No issues                                                                                                                                                                                                                                                                                 | Safe     |

| P <sub>3</sub> | Open         | Does not allow $P_1$ to turn off during self– check;<br>this can be detected as a fault status is triggered<br>on the FLT pin.                                                                                                                                                            | Safe     |

|                | Short        | <ul> <li>Pulls up the gate of P<sub>1</sub> consistently.</li> <li>Causes an inadvertent triggering of the desat fault.</li> </ul>                                                                                                                                                        | Safe     |

| R <sub>2</sub> | Open         | <ul> <li>This can be detected during self-check.</li> <li>The FLT pin is able to trigger a fault status but is unable to clear it.</li> </ul>                                                                                                                                             | Safe     |

|                | Short        | <ul> <li>Pulls down the gate of P<sub>1</sub> to ground and does<br/>not allow P<sub>1</sub> to turn off during self-check; this<br/>can be detected as a fault status is triggered on<br/>the FLT pin.</li> <li>Does not affect desat protection during normal<br/>operation.</li> </ul> | Safe     |

| R <sub>3</sub> | Open         | Does not allow $P_1$ to turn off during self-check;<br>this can be detected (FLT pin is able to set the<br>fault status but unable to clear it).                                                                                                                                          | Safe     |

|                | Short        | Does not allow $P_3$ to turn on (and $P_1$ to turn off);<br>this can be detected as a fault status is triggered<br>on the FLT pin.                                                                                                                                                        | Safe     |

| R <sub>4</sub> | Open         | Does not allow $P_3$ to turn on (and $P_1$ to turn off) during self-check; this can be detected as a fault status is triggered on the FLT pin.                                                                                                                                            | Safe     |

|                | Short        | No issues                                                                                                                                                                                                                                                                                 | Safe     |

| N <sub>1</sub> | Open         | Does not allow $P_3$ to turn on (and $P_1$ to turn off) during self-check; this can be detected as a fault status is triggered on the FLT pin.                                                                                                                                            | Safe     |

|                | Short        | Does not allow $P_3$ to turn off (and $P_1$ to turn off) during self-check; this can be detected as the FLT pin is unable to clear the fault status.                                                                                                                                      | Safe     |

| N <sub>2</sub> | Open         | A fault status is not triggered during self-check; this can be detected.                                                                                                                                                                                                                  | Safe     |

|                | Short        | the Cext is never discharged. Causes an inadvertent triggering of the desat fault.                                                                                                                                                                                                        | Safe     |

| R <sub>5</sub> | Open         | A fault status is not triggered during self-check; this can be detected.                                                                                                                                                                                                                  | Safe     |

|                | Short        | No issues.                                                                                                                                                                                                                                                                                | Safe     |

#### Table 2. FAILURE MODE ANALYSIS OF THE DESAT SELF-CHECK CIRCUIT FROM FIGURE 13

onsemi, ONSEMI, and other names, marks, and brands are registered and/or common law trademarks of Semiconductor Components Industries, LLC dba "onsemi" or its affiliates and/or subsidiaries in the United States and/or other countries. onsemi owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of onsemi's product/patent coverage may be accessed at <u>www.onsemi.com/site/pdf/Patent-Marking.pdf</u>. onsemi reserves the right to make changes at any time to any products or information herein, without notice. The information herein is provided "as-is" and onsemi makes no warranty, representation or guarantee regarding the accuracy of the information, product features, availability, functionality, or suitability of its products for any particular purpose, nor does **onsemi** assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using **onsemi** products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by **onsemi**. "Typical" parameters which may be provided in **onsemi** data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. **onsemi** does not convey any license under any of its intellectual property rights nor the rights of others. **onsemi** products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use **onsemi** products

#### ADDITIONAL INFORMATION

TECHNICAL PUBLICATIONS:

Technical Library: <u>www.onsemi.com/design/resources/technical-documentation</u> onsemi Website: <u>www.onsemi.com</u>

#### ONLINE SUPPORT: www.onsemi.com/support

For additional information, please contact your local Sales Representative at www.onsemi.com/support/sales